U.S. Department of Transportation

Federal Highway Administration

1200 New Jersey Avenue, SE

Washington, DC 20590

202-366-4000

Federal Highway Administration Research and Technology

Coordinating, Developing, and Delivering Highway Transportation Innovations

| REPORT |

| This report is an archived publication and may contain dated technical, contact, and link information |

|

| Publication Number: FHWA-HRT-12-072 Date: May 2013 |

Publication Number: FHWA-HRT-12-072 Date: May 2013 |

This chapter outlines the development details of an efficient wireless communication protocol between a moveable external reader and the embedded sensors.

For this project, researchers used an inductive coupling technique for remote RF powering and wireless communication with the sensor. Inductive coupling has been widely used for high-frequency (HF) RFID systems that operate below 30 MHz. The basic principle of inductive coupling is shown in figure 39 and figure 40 where inductor coil L1 is located on the reader and inductor coil L2 is located on the sensor. For this project, the operating frequency was chosen to be 13.56 MHz, which conforms to an existing HF RFID standard. When a 13.56-MHz signal is applied to antenna U1, a time varying magnetic flux is induced across inductor L2, and a voltage U2 is then established at the sensor due to mutual inductance M between the two coils. The mutual inductance M depends on the distance between the two inductors and their dimensions.

Figure 40 shows the equivalent circuit model for the RFID system and the load modulation scheme for wireless communication. R1 and R2 represent the coil resistances. R1, C1, and L1 form a serial resonance circuit for the reader, and R2, C2, and L2 form a parallel resonance circuit for the sensor. The resonance frequency of both circuits is set to be 13.56 MHz, thus maximizing the energy efficiency. The sensor impedance affects the observed voltage U0 at the reader. This voltage can be expressed as the equation in figure 41.

Figure 39. Illustration. Principle of HF RFID used in the sensing system.

Figure 40. Illustration. Equivalent circuit model for the RFID system and the load modulation scheme for wireless communication.

![]()

Figure 41. Equation. Input voltage.

Where:

i1 = Current in the reader resonance circuit.

ω = Resonance frequency.

RZ = Load resistance.

In the case of ohmic load modulation, a switch, S, is used to change the load resistance of the sensor. Two possible resistance values can be attached to the load, resistor RL (see figure 40), and resistors RL||RM (see figure 40). These two states are used for amplitude shift key (ASK) modulation between the reader and sensor for wireless communication.

The ASK modulation is achieved with a single NMOS transistor whose gate is connected to the data output of the sensor. In the design, the data are in a serial pattern from the ADC, which samples the source voltage of each FG channel. When data = 0, the NMOS transistor is turned off, and the resistor seen by the reader is Rsensor. When data = 1, the NMOS is turned on and the load resistor becomes 0. The different values of the resistor will change the amplitude of the RF signal. The design of the reader, shown in figure 42, is based on the TRF7960 chip from TI. TRF7960 is a fully integrated 13.56-MHz RFID front-end and data framing reader system. The 13.56-MHz crystal generates the local clock signal for the RF front end. The reader system can transmit the RF signal through the coil to the sensor and sense the variation of the envelope from the sensor part. The reader system is controlled by the field-programmable gate array (FPGA) for setting commands or receiving data.

Figure 42. Illustration. System-level architecture of the wireless communication system for the sensor.

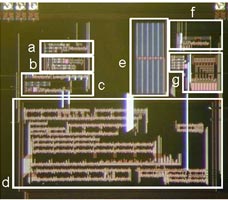

The system architecture of the sensor is shown in figure 43, and the micrograph of a CMOS prototype sensor is shown in figure 44. The core component of the sensor is the FG analog processor, which is self-powered by the piezoelectric transducer.

The communication module in figure 44 consists of: (a) ADC, (b) voltage multiplier, (c) demodulator and backscatter modulator, (d) high-voltage generator, and (e) digital base-band module (DBM).

Figure 43. Illustration. Architecture of the sensor.

Figure 44. Photo. Micrograph of the sensor prototyped in a 0.2-mil (0.5-μm) CMOS process.

The envelope recovery circuit used in the sensor is shown in figure 45. The voltage doubler implements a signal amplifier (gain equals 2), a rectifier, and a low-pass (cut-off frequency of approximately 200 KHz). Thus, the signal, V1, extracts the envelope from the received RF signal Vrf. Signal V1 is low-pass filtered by another resistor-capacitor cascade to obtain an average signal, V2. V1 and V2 are then compared using a comparator (highlighted in red), which produces a digitized version of the envelope.

Figure 45. Illustration. Envelope recovery module.

Figure 46 shows a simulation experiment where a 13.56-MHz RF signal was induced across the sensor antenna. The envelope of the RF signal is modulated by a random noise process. However, the comparator in previous versions of the sensor does not differentiate between envelope variations caused by ambient noise and envelope variations due to ASK modulation.

As a result, the compared recovers an envelope that matches the preamble and a valid command. This forces the state machine on the sensor to randomly switch states. In the newer version of the sensor, the problem was rectified by using a hysteretic comparator (see figure 47).

Figure 46. Graph. Output of the envelope recovery module using hysteretic and non-hysteretic comparators when a noisy RF signal is applied.

Figure 47. Illustration. Hysteretic comparator used in the improved envelope recovery circuit.

A comparator consists of cross-coupled NMOS transistors Q4 and Q5 (see figure 47), which introduce a dead zone where the comparator does not respond. The difference between the two input signals, Vin+ and Vin-, has to be greater than a certain value. Figure 46 (bottom two plots) shows the output of the envelope recovery module where the comparator does not produce any transition when the variations in RF signal envelope is small (less than 50 mV). Figure 48 shows the response of two envelope recovery modules (using conventional comparator and hysteretic comparator) for a 100 percent ASK modulated RF signal. The response shows that both modules can successfully decode the preamble and command. An additional advantage of using the hysteretic comparator is that it will reduce the output switching noise and the dynamic power dissipation of the system. Figure 49 shows the measured result obtained from the modified envelope recovery circuit (that includes the hysteresis comparator). The results show an improved demodulation performance.

Figure 48. Graph. Output of the envelope recovery module using hysteretic and non-hysteretic comparators when a valid ASK modulated RF signal is applied.

Figure 49. Illustration. Measured output of the envelope recovery module using hysteretic and non-hysteretic comparators when a valid ASK modulated RF signal is applied.

ADC selects each channel of the FG processor and encodes the stored parameter into a digital encoded data. In this prototype, there is an 8-bit single-slope ADC on the sensor. The structure of the ADC is shown in figure 50 . Before the conversion starts, S1 is zero, and the voltage on the storage capacitor Cst is charged to the input voltage Vin. When the conversion is triggered by setting S1 to 1, Cst is disconnected to the input, and a constant current source Idis begins to discharge the capacitor. Assuming the current is constant, the discharging speed of Vst is also constant. Meanwhile, the 8-bit counter is triggered by S1 and records the total discharging period from Vin to Vreg. When Vst is reduced below Vref, the output of the comparator is reserved, and the counter stops. The residential value in the counter can be expressed as the equation in figure 51.

Figure 50. Illustration. Functional architecture of the single-slope ADC.

Figure 51. Equation. Residential value in the counter.

Where:

fclk = Clock frequency for the counter.

In figure 50, the bias current of the comparator is set to be 1.5 μA, which insures that the total power consumption of the ADC is low.

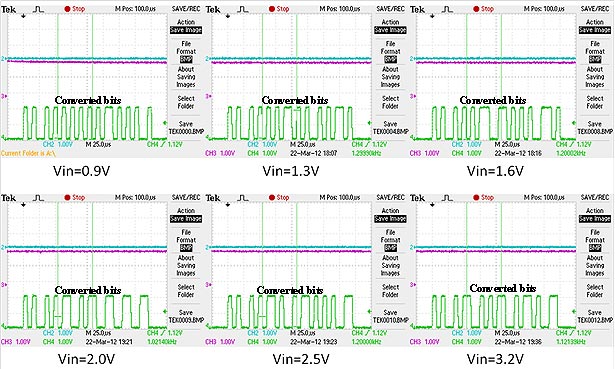

Improvements to the ADC were also performed by using large-size integrating capacitors and introducing a topology of a sample-and-hold circuit to reduce the effect of channel charge injection and clock feedthrough. Figure 52 shows the measured responses from the fabricated ADC when its input voltage is varied.

Figure 52. Graph. Digital output stream produced by the ADC when the input voltage is varied.

In most RF power harvesting systems, the amplitude of the induced RF signal from the antenna is usually small and is not enough to operate any other circuit components. The voltage multiplier is employed to boost the weak signal to a sufficiently high level and to build charge on an on-sensor capacitor. The structure of the multiplier is based on the Dickson voltage multiplier architecture in figure 53 . Using the diodes, the current is only allowed in the direction that charges the capacitor in the next stage. For a multiple-stage voltage multiplier, the output voltage can be expressed as shown in figure 54.

Figure 53. Illustration. Structure of the Dickson voltage multiplier.

Figure 54. Equation. Output voltage.

Where:

C = Storage capacitor.

Cpar = Parasitic capacitor.

Von = Turn-on voltage for the diode.

Vload = Additional voltage drop depending on the load current.

The induced RF signal Vrf is typically less than 1 V. As a result, diodes with large turn-on voltage significantly decrease the generated voltage. The diode is usually replaced by a diode-connected transistor in the design, so a low-threshold or zero-threshold transistor is preferred for the voltage multiplier. When the low-threshold process is not available, using a Schottky diode is another option to reduce Von. A group of Schottky diodes with a different number of fingers and same junction area have been fabricated in a 0.02-mil (0.5-μm) standard CMOS process. The diode with more fingers shows smaller Von due to the reduction of the parasitic resistor. However, the reversed current will also increase for the diode with more fingers. All the turn-on voltages for Schottky diodes are measured to be close to 300 mV, which is much less than Vth for the process (0.7 for NMOS and -0.9 for PMOS).

The demodulator module on the sensor is used to acquire command and control information (also known as forward link) from the reader, whereas the backscatter modulator is used to modulate the impedance of the coil and establish a reverse link communication from the sensor to the reader. The system architecture implementing the demodulator and backscatter modulator is shown in figure 55. In the forward link from the reader to the sensor, a pulse width modulation (PWM) approach is used, where a pulse width of 75 ms indicates 1 and a pulse width of 50 ms indicates 0. When the reader is sending a command, the variation on the RF envelope can be detected. The recovered pulse signal itself resets the integrator and generates a different level according to the pulse width. Afterwards, a level crossing decodes the received bit. For the backward link from sensor to reader, a simple backscatter scheme is applied. After the voltage is sampled by the ADC, the result is encoded to a serial Manchester code for transmission. The transmitted data are directly applied to the gate of the backscatter NMOS transistor. The equivalent impedance seen from the antenna is changed when the NMOS transistor is turned on/off. Such difference results in a variation on the RF envelope which can be sensed by the reader.

Figure 55. Illustration. Function blocks of the modulator and demodulator.

Initializing and configuring FG transistors in the analog processor requires on-chip, high-voltage generation (> 17 V for FN tunneling and > 5 V for hot electron injection). This is challenging because the CMOS fabrication process chosen for this project supports only n-well isolation, and the rated break-down voltage of the oxide layers is approximately 8 V. Researchers implemented a high-voltage generator using a modified Dickson charge-pump architecture (see figure 56 and figure 57). Each stage of the charge pump consists of bulk-driven PMOS diodes, which are driven by non-overlapping clocks. Like a Dickson charge-pump, in each clock-cycle, charge builds up at the intermediate capacitor and the PMOS circuit provides bulk isolation from other on-chip supply voltages. Thus, the proposed charge pump can generate voltages as high as 20 V. This has been verified using measurement results from a fabricated prototype, and a sample result is shown in figure 58. The generated voltage has a monotonic relationship with respect to the frequency of the non-overlapping clocks because higher the frequency the faster charge can be transferred between stages of the charge pump.

Figure 56. Illustration. Charge pump used for implementing the high-voltage generator.

Figure 57. Illustration. Timing diagram of the non-overlapping clock generator.

Figure 58. Graph. Sample results from fabricated prototype.

The DBM decodes the commands received from the reader and implements a state machine, which controls the configuration, initialization, and communication functions of the sensor. The functional architecture of the DBM and the state machine implemented by the DBM is shown in figure 59.

Figure 59. Illustration. State machine implemented by DBM.

The state machine is implemented with standard CMOS logic, and the architecture has been synthesized using the standard logic synthesis procedure. By default, the state machine is in its ideal state, S0. Transition to the other states (S1–S5) occurs when a valid command is received from the reader. The validity of the command is confirmed when the data packet transmitted from the reader is Manchester encoded and satisfies the parity check condition.

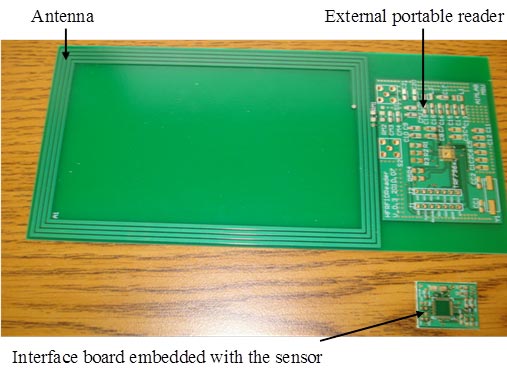

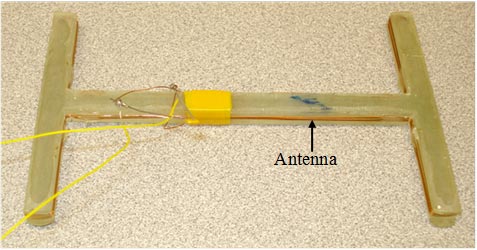

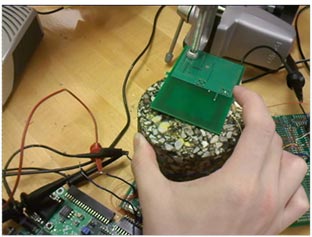

Prototype sensor ICs have been fabricated in a 0.02-mil (0.5-μm) standard CMOS process. The total area of the sensor IC is 0.06 × 0.06 inches (1.52 × 1.52 mm), which was then integrated on a custom-made printed circuit board (PCB) as shown in figure 60. In order to optimize the power transfer and increase the reading distance, an external reader was designed and manufactured (see figure 60). The design is based on a commercial chip TRF7960 from TI, which is a fully integrated 13.56-MHz RFID analog front-end system. The TI chip is controlled by an FPGA that has been programmed for data encoding and decoding. The reader interfaces with an embedded antenna, which fits the exact H-shape of the designed package, thus establishing a link for data transfer (the embedded antenna is shown in figure 61). The antenna is connected to the board shown in figure 60 along with the external reader to illustrate the size difference. Laboratory testing showed that the reading distance highly depends on the parasitic capacitances of the antennas and the manufactured sensor, varying between 1 and 13 inches (25.4 and 330.2 mm). These capacitances are manufacturing process dependent. As a result, individual calibration is required as well as testing under field conditions in order to assess the exact performance.

Figure 60. Photo. Manufactured external reader and internal interface board.

Figure 61. Photo. Second prototype antenna adapted to the H-shaped gauge.

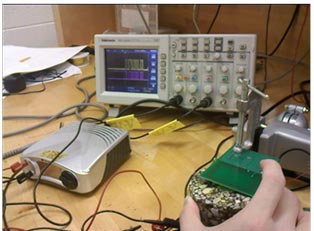

For the evaluation, the protocol processing block in TRF7960 was disabled, and another FPGA development board (SPARTAN®-3) was designed as the digital transceiver for the reader. TRF7960 was working under direct mode where the PWM data were modulated onto the 13.56-MHz RF carrier with 100 percent ASK modulation. The received data from the sensor can be detected and recovered into digital form after noise filtering and digitizing. Figure 62 and figure 63 show measured results for the ASK modulation. In figure 62, channel 2 is the sample output from ADC. It consists of the valid preamble, 8-bit data, and a 3-bit cyclic redundancy check (CRC). The data are encoded to Manchester code for transmission. Channel 3 represents the envelope variation of the RF signal. When the data equal 1 (binary code), the amplitude of the RF signal is close to 0 since the NMOS transistor shorts the load resistor to ground. When the data are 0, the amplitude of the RF signal is high. Figure 63 shows a close-up image of figure 62.

Under matching conditions, the transmitted output power from the reader is 200 mW (23 dBm) when referred to a 50-ohm load at 5 V. In the measurement, the sensor used the same coil antenna as the reader, and it was measured to be powered by the RF signal at a distance of 16 inches (406.4 mm). All the function of the control logic has been verified in interrogating mode. As shown in figure 64 and figure 65, the transition between the readout and injection state is presented according to the state machine in figure 59. As shown in figure 61, before the command to inject the FG channel is sent, the channel was within the 2–3 V range. After the injection command was recovered by the RF front end, the channel voltage increased beyond 4 V for hot electron injection. Figure 65 shows a sample result where the on-chip high-voltage generator is activated after a tunneling command is received by the sensor. The result shows that the output voltage increases to about 15 V within 625 ms. Note that a 10-M load resistance was connected at the output of the charge pump, which indicates that the open-load voltage is significantly higher and sufficient for tunneling.

Figure 62. Illustration. Measured results for ASK modulation.

Figure 63. Illustration. Close-up view of measured results for ASK modulation.

Figure 64. Illustration. Measured results showing the sensor entering into an injection state.

Figure 65. Illustration. Measured results showing the sensor entering into a tunnel state.

Figure 66 shows a sample result where the command was sent from the reader to remotely acquire the magnitude of the voltage stored on a FG injector channel. After the integration time required by the ADC, the 8-bit digitized result was packetized with valid preamble and 1-bit CRC code. The data packet was then communicated from the sensor to the reader using backscatter modulation using a series Manchester code. Figure 67 shows a sample result where the data on the sensor are continuously sampled (when the sensor is in state S5). As a result, the data stored in all the FG channels are digitized and backscattered to the reader sequentially.

Figure 66. Illustration. Measured results showing the sensor data received by the reader when it sends an acquire command.

Figure 67. Illustration. Measured results showing multi-channel sensor data received by the reader when the sensor is in a continuous sampling state.

To test the communication protocol at the selected frequency, a set of preliminary tests were conducted. Signals were sent through concrete and asphalt (see figure 68 through figure 72). The digital command sent from the reader to the sensor was received in both cases. The feedback signal sent back from the sensor was completely recovered when transmitted in concrete (see figure 73), but it presented a loss of information when sent in asphalt (see figure 74). The thickness of the concrete slab does not affect the accuracy of the recovered signal, while asphalt introduces a reading error due to its viscoelastic properties. The energy is dissipated in asphalt more than in concrete. This issue is solved by increasing the transmitted energy from the reader.

Figure 68. Photo. Sensor placed under a concrete specimen.

Figure 69. Photo. Receiver placed on top of the concrete specimen.

Figure 70. Photo. Concrete specimen placed between a reader and receiver.

Figure 71. Photo. Test setup with an asphalt concrete (AC) specimen introduced between the reader and the receiver.

Figure 72. Photo. Oscilloscope showing the voltage measured at the receiver.

Figure 73. Illustration. Communication signals transmitted through concrete.

Figure 74. Illustration. Communication signals transmitted through asphalt.

As anticipated, the system integration of the sensor and the wireless communication protocol was one of the most challenging tasks in this study. Given the unique nature of the sensing system and based on analog FGs, an adapted and equally unique wireless protocol was completely designed and tested.

A major glitch in the high-voltage generation module caused delays, given that several versions had to be manufactured and tested. The CMOS fabrication process used for this project supports only n-well isolation, and the rated break-down voltage of the oxide layers is approximately 8 V, preventing the generation of the 18 V required for the initialization of the memory gates. After several iterations, a successful design was achieved (details are described in section 3.2.4).

As shown in figure 60 and figure 61, specific antennas were designed and manufactured for this particular system (commercially available antennas and readers cannot be used because of the low power levels at which the sensor operates). The reading distance from the sensor depends on the tuning of the wireless links for maximum power transfer, which depends on the parasitic capacitances of the antennas (embedded antenna and external reader) as well as the parasitic capacitance at the sensors' input. These capacitances are induced by the manufacturing process. The reading distance at which the system can operate (and thus the installation strategy) depends on the tuning outcome under specific field conditions.

Some research focused on optimizing the matching network that can maximize the read and powering distance to the sensor. The design flow is summarized in figure 75, where Rs, RL, and CL denote the reader impedance, sensor load resistance, and sensor load capacitance, respectively. Q_reader and Q_tag denote the quality (Q)-factor of the reader and the sensor, which, in-turn, determines the sensitivity of the reader. Vr, Ir, Vt, It, PRs, and PRL denote the internal electrical variables (voltage, current, and power) at the reader and sensor based on the antenna dimensions, structure, and material properties including the propagation properties of the ambient environment.

Figure 75. Flowchart. Design flow to optimize the matching network that can maximize the powering and reading distance between the sensor and the reader.

Figure 76 and figure 77 show the sample results obtained from the design flow for a 13.56-MHz RF back-telemetry system (see figure 75). Figure 76 shows that for a 300-ohm sensor load, the maximum powering distance occurs at 8 inches (203.2 mm), whereas figure 77 shows the voltage induced at the reader when the distance between the reader and sensor is varied. These figures can be used to calibrate the electrical circuit on the sensor IC.

Researchers developed a reactive voltage-boosting technique that can be used to overcome threshold voltage limitations (and hence powering distance) imposed by voltage multipliers in an energy scavenging sensor. Experimental results have shown significant improvements in powering distance, which makes the proposed method attractive for implementing long-range inductively coupled RF sensors.

Figure 76. Graph. Simulation results showing the power received at the sensor when the sensor-reader distance is varied.

Figure 77. Graph. Simulation results showing the voltage induced at the sensor when the sensor-reader distance is varied.

Several circuit techniques have been proposed to optimize the power transfer efficiency in an inductively powered sensor. However, when high throughput for data transmission between the sensor and the reader (or vice versa) is not required, then the Q-factor of the energy scavenging frontend can be traded off with the communication bandwidth according to the Bode-Fano limit. This is the case for the hybrid scavenging sensor, where mechanical events are asynchronously sensed, computed, and stored without the requirement of real-time transmission. Enhancing the Q-factor of the energy scavenging front-end has an added benefit in that it also overcomes the minimum voltage (threshold voltage) requirement for jump-starting the voltage multiplier circuits in the sensor. The efficiency of the voltage multiplying and the regulation circuit significantly improves when the input voltage is larger than the threshold voltage. Therefore, the proposed reactive voltage-boosting approach enhances the powering distance of the sensor when compared to the traditional matching techniques.

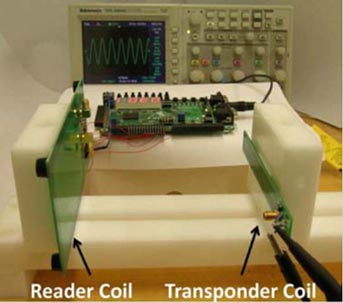

The performance of the proposed voltage-boosting method has been verified using the experimental setup shown in figure 78 in which the 13.56-MHz reader and the sensor are separated by an adjustable distance. The reader and the sensor coils have been fabricated on a planar PCB. The reader coil is driven by a TRF7960 chipset with a maximum output power set to 200 mW.

The voltage multiplier and sensor circuits are modeled by a load capacitance CL with a variable resistance RL which is inversely proportional to the power dissipation of the sensor (see figure 79). RL can also be obtained from the I-V curve in figure 80, which shows the diodic response of a typical voltage multiplier. When the input voltage VL is below the threshold voltage VON, the effective RL is large, and the multiplier is unable to boost the input voltage, resulting in ultra-low power conversion efficiency. When VL is greater than VON, RL is small enough to facilitate proper operation of the multiplier at the rated conversion efficiency. The purpose of the series matching circuit is to pre-boost VL to overcome the threshold voltage VON of the multiplier. For the proposed series matching on the transponder side (see figure 79), the sum of CP and CL should resonate with LS and CS should resonate with Lt. At 13.56 MHz, the input impedance of the sensor was measured to be CL = 72pF in parallel with RL = 200 ohm. To compare the performance of the proposed matching network, a sensor which integrates the previous parallel matching network was used as a benchmark. Therefore, for parallel matching, CP was set to 68 pF to resonant with 0.94 μH of Lt; for proposed matching, Cs was set to 140 pF, LS was chosen to be 180 nH, and CP was set to 650 pF.

Figure 78. Photo. Experimental setup used to validate the proposed reactive voltage-boosting method.

Figure 79. Illustration. Equivalent circuit model for the setup.

Figure 80. Graph. Non-linear resistive model for the voltage multiplier on the sensor IC.

The measurement results using an 18-stage loaded Schottky multiplier (for analog circuits) are shown in figure 81, where the inset shows the same response in logarithmic scale. These results show that the proposed approach can significantly boost the voltage compared to the previously used parallel matching approach. Note that the maximum output voltage of the Schottky multiplier is limited by the over-voltage protection diodes integrated on the sensor IC. Figure 82 compares the measured response obtained from a 12-stage multiplier (used for powering digital circuits). Again, the results show that the proposed matching can achieve higher output voltage.

However, compared to the results in figure 81, the improvement is not significant, which is attributed to the minimum threshold voltage required for powering the Schottky multiplier and higher load current required for driving the digital circuits.

Figure 81. Graph. Comparison of the voltage generated by an 18-stage voltage multiplier for the new and previously used matching network.

Figure 82. Graph. Comparison of the voltage generated by a 12-stage voltage multiplier for the new and previously used matching network.

This chapter describes the design and development of a novel RF communication module. The mixed mode module is specific for integration with the FG analog memories. The RF powering mode is dissociated from the computing and storage circuitry and is achieved by harvesting the RF signal. The salient modules of the RF module include the following:

In addition, an external reader was designed and manufactured. The reader interfaces with an embedded antenna, which was also designed and manufactured in-house and fits the exact H-shape of the designed package. The embedded antenna is connected to the interface. Laboratory testing showed that the reading distance highly depends on the parasitic capacitances of the antennas (embedded antenna and external reader) as well as the parasitic capacitance at the sensors input. These capacitances are induced by the manufacturing process and cannot be predicted upfront. A calibration procedure and antennas resonance tuning is required.